JEDAT社およびパートナー企業の DAC2014 出展情報について

株式会社ジーダット

イベント情報

お客様各位

2014年5月8日

株式会社ジーダット

JEDAT社およびパートナー企業の DAC2014 出展情報について

来る2014年6月2日から4日まで、米国サンフランシスコにて開催されます「51回 DAC(Design Automation Conference)」において、当社および、パートナー各社は、下記の通り展示・デモを行います。

DACにお越しの際は、是非各社ブースにお立ち寄りくださいますようお願い申し上げます。 デモのご予約は下記メールにて受け付けておりますので、お手数ですが事前連絡をお願いいたします。

Jedat Inc. Booth: #2305

■ Reuse-based Analog Synthesis アナログ回路・レイアウト合成ツール

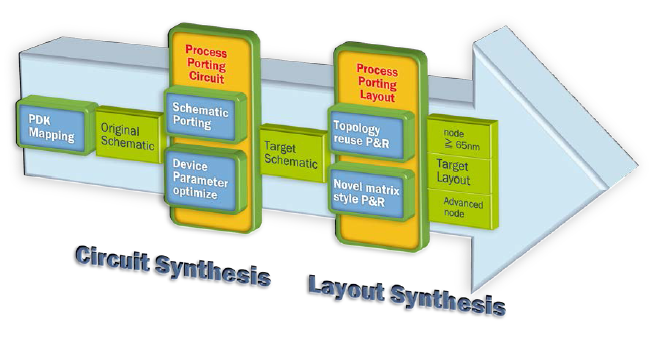

再利用メソドロジを利用し、最先端プロセスに適用可能な自動設計手法で、設計品質およびTATの改善が可能になります

オリジナルな設計データを利用し、ターゲットプロセスへのポーティングでの、設計者に予測可能な回路・レイアウト設計データを自動生成します。

最先端テクノロジでは、FinFETでのレイアウト制約を考慮した、マトリックス・アレー形式の自動レイアウトに対応します。

これらのツールは、次の4つのタスクに分かれ、ユーザは設計でのクリティカルな工程に利用することができます。

また、これらはOAベースのツールですので、現在の設計環境を変更する必要はありません。

- PDK Mapping and Schematic Porting

- Circuit Optimizer

- Topology Reuses P&R

- Novel Matrix-Style P&R

■ Vela-iDRC 高速・高精度インタラクティブDRC

- Vela-iDRCは、高速な階層DRCおよびマルチスレッディングにより、大規模・先端データをインタラクティブに高速・高精度な解析・デバッグを可能とします。

- αSX Ismoと連携することで、複雑なDRCエラーを高速検証・データ検索および編集するという ループを短時間で回し、迅速なテープアウトを可能とします。

- 検証エンジンをサーバーに、編集環境をローカルにすることで設計環境の有効利用が図れます。

EDXACT SA Booth: #527

寄生効果によるSpiceネットリストの規模増大の課題を、現存のツールフローをそのままにして、実績のあるmathematics-based な縮退ツールJivaroにより解決します。

下記の機能をエンハンスしています。

- 温度相関性を保った抵抗の縮退

- モデル込の抵抗の縮退

- 並列ネットの探索と併合

- アクティブ素子の縮退

さらに、次の2つのツールををご紹介します。

- Belledonne:

2つの抽出されたネットリストを、寄生RCやRC遅延への影響という観点でバッチ的に比較します。 - Viso:

抽出後の指定ポイント間のRC delay、総容量、また各層のRCdelayへの貢献度などのレイアウト解析を行います。

FishTail Design Automation, Inc. Booth: #1725

SDC制約のフォーマル検証の品質・機能向上をご紹介します。 Fishtailは、どのようなデザインのサイズ・論理の複雑さに対しても、例えば下記のような機能をご提供できる唯一のEDAベンダーです。

- generated clockで指定されたperiodの設計における機能との整合性の検証

- multiple combinationalピンに指定されたcase analysisの、これらをドライブする論理との一貫性の検証

- クロックが論理的に相互にexclusiveか否かの検証

- デザインとしての機能やアーキテクチャとして、マルチサイクルパスが正しいか否かの検証、そしてすべてのマルチサイクルパスによるパス制約を検証します。

さらに、ライセンスやマシン数、さらには合成・P&R・STAの実行時間を削減できる、SDCのmode-merging機能をご紹介します。

また、clock browser/ constraint debug environmentをご紹介します。

Runtime Design Automation Booth: #1625

リソース管理、プロセス自動化、そして設計最適化と3つのテーマで出展します。リソース管理では LicenseMonitor/NetworkComputerによる計算機/ライセンス資源の最適化、プロセス自動化ではFlowTracerによる効率的なツール実行を対案します。

さらに今回初めてスイートを設置し、次の3つのFlowApps(アプリ)をご紹介します。

■ Functional Coverage:ランダムテストの新しいカバレッジ手法

■ Libray/IP Delivery:スケーラブルなライブラリ/IPの新しい配布手法

■ QoR Convergence:斬新的なQoR手法

なお、スイート・プログラムの聴講には事前登録が必要です。

Silicon Frontline Technology Booth: #1719

SoCやIPなどのIC設計のための高性能な設計データ管理ツールを展示します。

■ パワーデバイス解析

- Ethan (Electro-thermal analysis)

Ethanによる信頼性と効率向上に向けた適用事例についてご紹介 - R3D

最新のプロセスノードを含め複雑なパワーデバイスへの適用についてご紹介 - R3DGate

高速パワーデバイスほど重要となるゲート遅延解析と最適化の実現

■ ESD解析(ESRA)

- ESRAが持つ独自のESD解析機能、採用される理由等についてご紹介

- 新機能であるESD保護素子以外の通常デバイスの破壊強度解析

- ESDデバイスに対する解析機能

■ IR Drop、エレクトロマイグーション解析

- IR Dropやエレクトロマイグーションの危険性をチェック

- レイアウトデータのみによる早期段階からチェックを実現

- 新機能である結線全体の抵抗マップ表示についてご紹介

■ 寄生抽出

- 高精度を保証したフルチップ抽出手法についてご紹介

- ネットごとの要求精度に応じた抽出を実現、最適な解析手法を提供

皆様のご来場をお待ち申し上げております。

お問い合わせ、ご予約は こちらまでお願いいたします。

以上

Download

Download